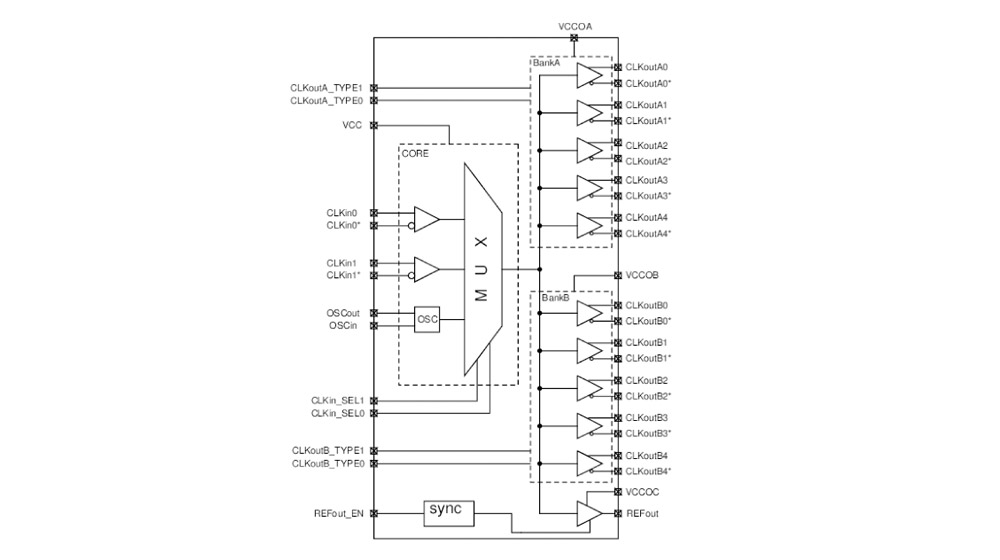

• Inputs can be LVPECL, LVDS, LVCMOS, SSTL, HCSL and XTAL waveforms.

• Crystal frequencies from 8 MHz to 50 MHz are supported

• Three output driver banks operating independently with 2 banks of LVPECL, LVDS, HCSL or HIZ and a single LVCMOS output available.

• Typical output skew between clock outputs is 30 ps

• Level translation with core supply voltage of 3.3 V/2.5 V and output supply voltage of 3.3 V/2.5 V/1.8 V

• Wireless and Wired Infrastructure

• Networking and Data Communications

• Medical equipment

• Automation and test equipment

• High-End Audio/Video

• Low additive jitter and low output-to-output skew ideal for jitter/phase sensitive applications

• Wide operation voltage for design compatibility

• Low power consumption ideal for portable and high density applications