# AU5325: 10 Outputs, Quad PLL Frequency Translation, Jitter Attenuator

## **General Description**

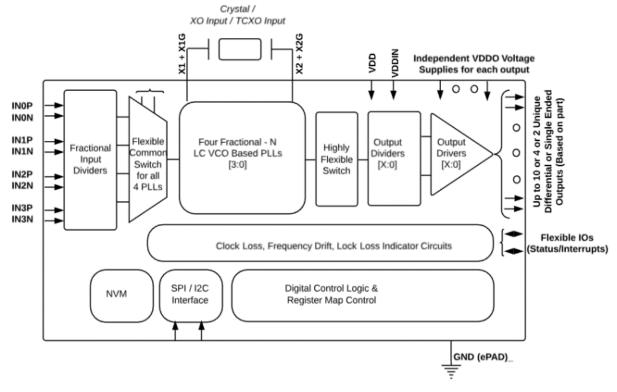

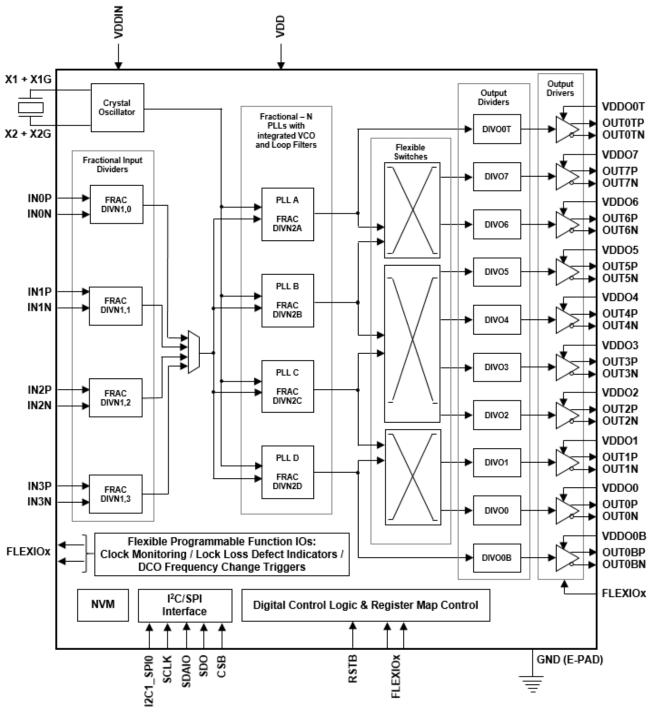

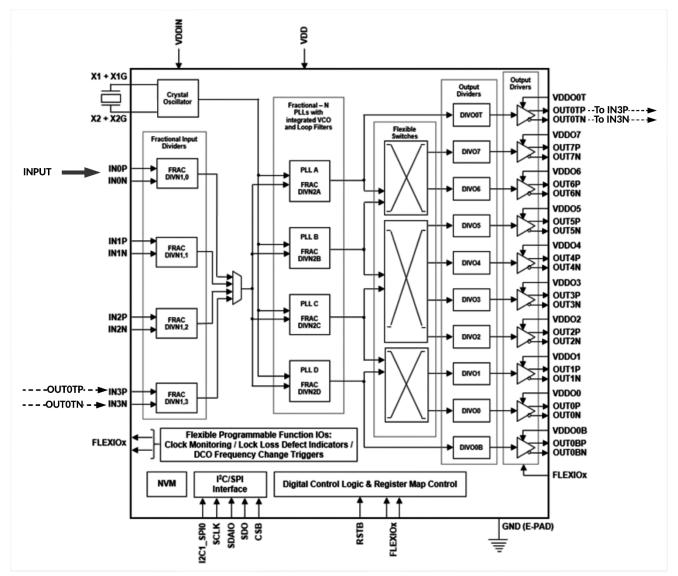

AU5325 is a programmable Quad Fractional Frequency translation based jitter attenuating clock synthesizer parts with flexible input to output frequency translation options. It supports up to 4 input clocks that are common for all the 4 fractional translations and provides 10 clock outputs. The clock outputs can be derived from the 4 PLLs in a highly flexible manner.

They are fully programmable with the I2C/SPI interface or an on chip, two time programmable, non-volatile memory for factory pre-programmed devices.

Using advanced design technology, they provide excellent integrated jitter performance as well as low frequency offset noise performance while working reliably in the ambient temperature range from -40 °C to 85 °C. The chip has best-in-class transient performance features in terms of clock switching transients and repeatable input to output delays.

#### Nomenclature:

AU5325BC1:VDDIN=3.3V,VDD=1.8V/2.5V/3.3V, VDDIO = VDD AU5325BC2:VDDIN=3.3V,VDD=1.8V/2.5V/3.3V,VDDIO = VDDIN

#### Applications:

- · Carrier Ethernet,

- · OTN Equipment,

- Microwave Backhaul,

- · Gigabit Ethernet,

- Wireless Infrastructure,

- Network Line Cards,

- · Small Cells,

- Data Center/Storage,

- SONET/SDH,

- Test / Instrumentation,

- Broadcast Video

### **Features**

- Flexible quad PLL frequency translation from a common input: 4 fractional output domains from single input

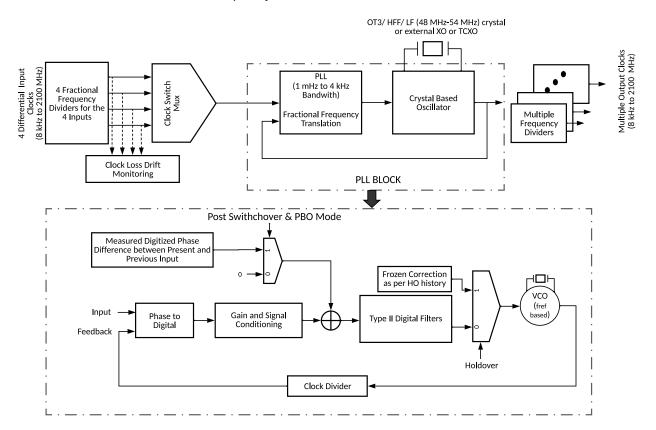

- Fully Integrated Fractional N PLLs with integrated VCO and programmable loop filter (1 mHz to 4 kHz)

- Wide frequency support

- o Differential Output from 8 KHz to 2.1 GHz

- o Single Ended Output from 8 KHz to 250 MHz

- o Support for 1 Hz frequency on one output

- o Differential Input from 8 KHz to 2.1 GHz

- o Single Ended Input from 8 KHz to 250 MHz

- o Multiple Crystals / XO / TCXO / OCXO support

- LVPECL, CML, HCSL, LVDS and LVCMOS Outputs

- 150 fs typical rms integrated jitter performance

- Synchronized, holdover or free run operation modes

- Meets G.8262 EEC Option 1,2(Sync E)

- Hitless input clock switching: Auto or manual

- o Sub 50 ps phase build out mode transients

- Phase Propagation with programmable slopes

- Frequency ramp for plesiochronous clocks with programmable slopes

- Robust and fast cycle slip and frequency step detection for input frequency steps (Clean frequency tracking for large frequency steps)

- Excellent Close-in Phase noise performance with no external discrete VCXOs or passive external filters

- Digitally Controlled Oscillator mode: to 0.005 ppb

- Programmable Output Delay Control

- Programmable Frequency Ramp Slopes for Switching Pleisochronous Clocks

- Indicators: Lock Loss, Clock Loss, Frequency Drift

- Repeatable Input to Output delays for each power up of chip

- Zero Delay Buffer mode also possible on any one PLL

- Output wake up sync with an independent clock also possible

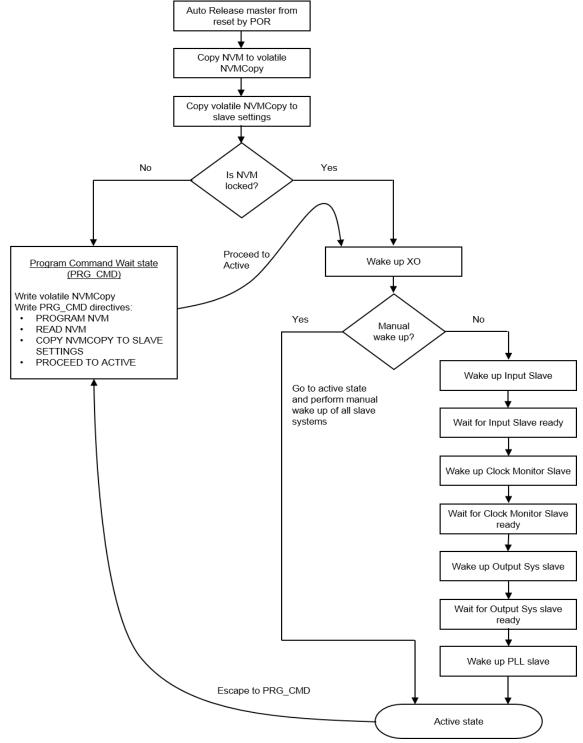

**Figure 1 Functional Overview**

# **Table of Contents**

| General Description                                                                                    | 1  |

|--------------------------------------------------------------------------------------------------------|----|

| Features                                                                                               | 1  |

| Table of Contents                                                                                      | 3  |

| List of Tables                                                                                         | 5  |

| List of Figures                                                                                        | 6  |

| 1 Pin Description                                                                                      |    |

| 2 Electrical Characteristics                                                                           |    |

| 3 Functional Description                                                                               |    |

| 4 Master and Slaves: Architecture Description and Programming Procedures                               |    |

| 5 Input Slave Description                                                                              |    |

| 6 Clock Monitor Slave Description                                                                      |    |

| 6.1 Fault Monitoring                                                                                   |    |

| 6.1.1 Clock Loss Monitors                                                                              |    |

| 6.1.2 Frequency Drift Monitors                                                                         | 32 |

| 6.1.3 Lock Loss Monitors                                                                               |    |

| 6.1.4 XO Clock Loss Monitors                                                                           |    |

| 7 Output Slave Description                                                                             |    |

| 8 PLL Slave Description                                                                                | 35 |

| 9 PLL Input Selection: Manual and Hitless Switching                                                    | 36 |

| 10 Zero Delay Mode                                                                                     | 37 |

| 11 PLL Bandwidth Control                                                                               | 38 |

| 12 PLL Crystal Clock Reference                                                                         | 39 |

| 13 PLL Lock Loss Defect Monitoring                                                                     | 40 |

| 14 PLL DCO Mode operation                                                                              | 41 |

| 15 Programmable Interface Top Level View                                                               |    |

| 16 Serial Programming Interface Description                                                            |    |

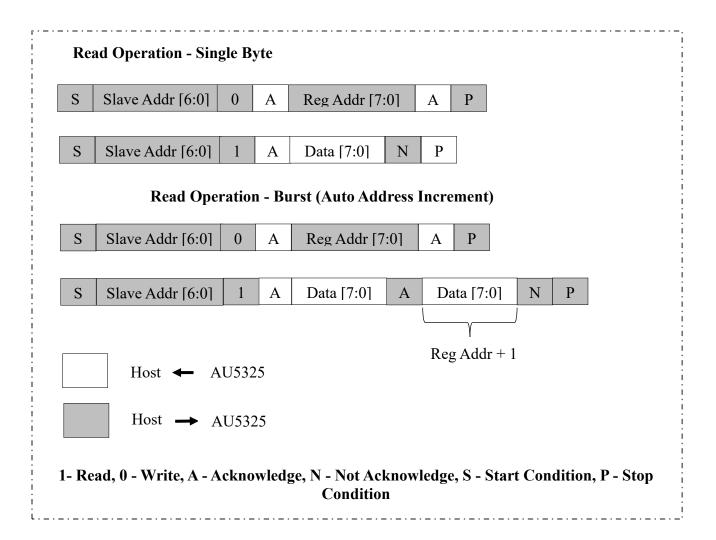

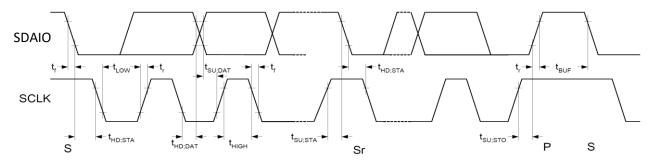

| 16.1 I2C protocol                                                                                      |    |

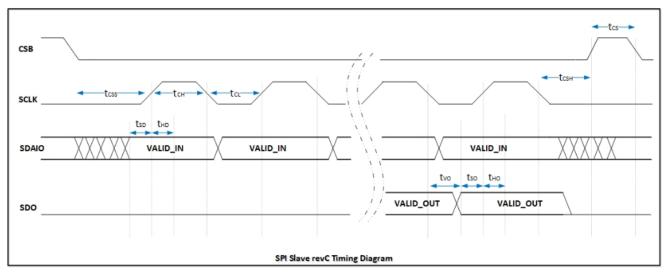

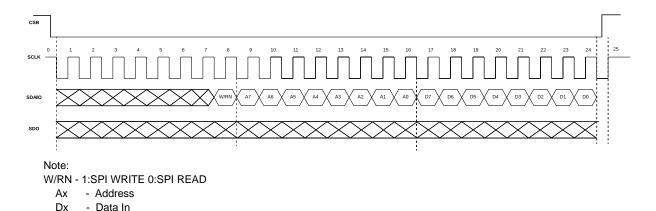

| 16.2 SPI Protocol                                                                                      |    |

| 16.3 SPI Timing Details                                                                                |    |

| 16.3.1 SPI Single byte write                                                                           |    |

| 16.3.2 SPI Single byte read                                                                            |    |

| 17 Package Information                                                                                 |    |

| 18 Output Termination Information                                                                      |    |

| 19 Input Termination Information                                                                       |    |

| 20 Crystal Pathway Connectivity Options                                                                |    |

| 21 Monitoring through the register map read back: Status and Notify                                    |    |

| 21.1 Tabular Listing                                                                                   |    |

| 21.2 Examples for Live Status Read Back                                                                |    |

| 21.3 Examples of Sticky Bit Clearing                                                                   |    |

| 22 Device Initialization for non-programmed device                                                     |    |

| 23 Monitoring the Status for Master and Slave Pages                                                    |    |

| 24 Programming the Primary E-Fuse                                                                      |    |

| 24.1 Configuration Bits to Force Power-up of Digital Slave Subsystems                                  |    |

| 24.2 E-Fuse Lock Configuration Bits                                                                    |    |

| 24.3 E-Fuse Write Configuration Bits24.4 Configuration Bit to Remove Manual Wake Up for Primary E-Fuse |    |

| 24.5 Pseudo Code: Programming the Primary E-Fuse                                                       |    |

| 24.5.1 GENERIC_SYS                                                                                     |    |

|                                                                                                        |    |

| 24.5.2 INPUT_SYS                                                                   | 82  |

|------------------------------------------------------------------------------------|-----|

| 24.5.3 CLKMON_SYS                                                                  | 82  |

| 24.5.4 OUTPUT_SYS                                                                  |     |

| 24.5.5 PLLA_SYS                                                                    | 83  |

| 24.5.6 PLLB_SYS                                                                    | 83  |

| 24.5.7 PLLC_SYS                                                                    | 83  |

| 24.5.8 PLLD_SYS                                                                    |     |

| 24.5.9 Removing Manual Wake-up and Locking GENERIC_SYS E-Fuse                      | 84  |

| 25 Programming the Secondary E-Fuse                                                | 85  |

| 25.1 Configuration Bit To Escape To PROGRAM_CMD State in GENERIC_SYS               | 85  |

| 25.2 Configuration Bit to Change the E-Fuse pointer                                |     |

| 25.3 Configuration Bit to Enable Manual Wake Up for Secondary E-Fuse               | 85  |

| 25.4 Psuedo Code: Programming the Secondary E-Fuse                                 | 86  |

| 25.4.1 GENERIC_SYS                                                                 | 86  |

| 25.4.2 INPUT_SYS                                                                   |     |

| 25.4.3 CLKMON_SYS                                                                  | 87  |

| 25.4.4 OUTPUT_SYS                                                                  |     |

| 25.4.5 PLLA_SYS                                                                    |     |

| 25.4.6 PLLB_SYS                                                                    |     |

| 25.4.7 PLLC_SYS                                                                    |     |

| 25.4.8 PLLD_SYS                                                                    |     |

| 25.4.9 Programming GENERIC_SYS E-Fuse to Remove Manual Wake Up in Secondary E-Fuse | 89  |

| 26 Register Map Details                                                            |     |

| 27 Ordering Information                                                            |     |

| 28 Revision History                                                                | 119 |

|                                                                                    |     |

# **List of Tables**

| Table 1 Pin Description                                                              | 8   |

|--------------------------------------------------------------------------------------|-----|

| Table 2 Absolute Maximum Ratings                                                     | 12  |

| Table 3 Operating Temperatures, Thermal Characteristics and Environmental Compliance | 12  |

| Table 4 DC Electrical Characteristics                                                | 12  |

| Table 5 Input Clock Characteristics                                                  | 14  |

| Table 6 Serial and Clock Input                                                       | 14  |

| Table 7 Output Serial and Status Pin                                                 | 15  |

| Table 8 Output Clock Characteristics                                                 | 15  |

| Table 9 Fault Monitoring Indicators                                                  | 16  |

| Table 10 Crystal Requirements                                                        | 17  |

| Table 11 Output RMS Jitter in Frequency Translation Modes                            | 18  |

| Table 12 Close In Offset Phase Noise                                                 | 19  |

| Table 13 Power Supply Rejection                                                      | 19  |

| Table 14 Adjacent Output Cross Talk                                                  | 20  |

| Table 15 Output Clock Specifications                                                 | 20  |

| Table 16 PIF Description                                                             | 25  |

| Table 17 PIF Overview (Top Level Summary of the Programmable Interface)              | 42  |

| Table 18 I2C Bus Timing Specifications                                               | 46  |

| Table 19 SPI Timing                                                                  | 47  |

| Table 20 Tabular Listing of Alarm Registers                                          | 62  |

| Table 21 Configuration Bits to Force Power-up of Digital Slave Subsystems            | 80  |

| Table 22 E-Fuse Lock Configuration Bits for all pages                                | 80  |

| Table 23 E-Fuse Write Configuration Bits for All Pages                               | 81  |

| Table 24 Configuration Bit to Remove Manual Wakeup for Primary E-Fuse                | 81  |

| Table 25 Configuration Bit To Escape to PROGRAM_CMD State in GENERIC_SYS             | 85  |

| Table 26 Configuration Bit to change the E-Fuse pointer                              | 85  |

| Table 27 Configuration Bit to Enable Manual Wakeup for Secondary E-Fuse              | 85  |

| Table 28 Page 0: Generic Masters System Related Registers                            | 90  |

| Table 29 PAGE 1: Clock Monitor System Related Registers                              | 95  |

| Table 30 Input System Related Registers                                              | 101 |

| Table 31 Output System and Output Dividers Related Registers                         | 105 |

| Table 32 Page A: PLL A Related Registers (similar for Pages B, C and D)              | 113 |

| Table 33 Ordering Information for AU5325                                             | 118 |

| Table 34 Revision History                                                            | 119 |

# **List of Figures**

| Figure 1 Functional Overview                                                                         | 2  |

|------------------------------------------------------------------------------------------------------|----|

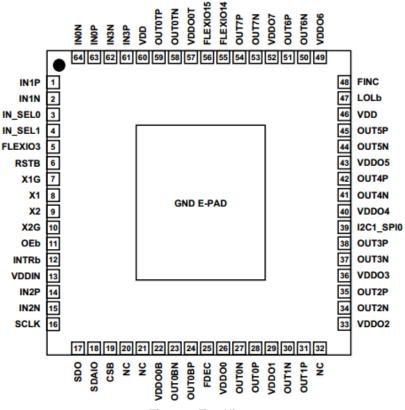

| Figure 2 Top View                                                                                    | 8  |

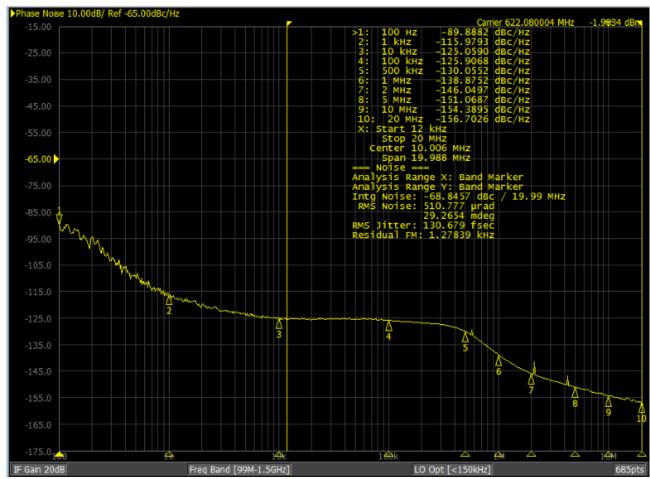

| Figure 3 Representative Phase Noise Measurement                                                      | 18 |

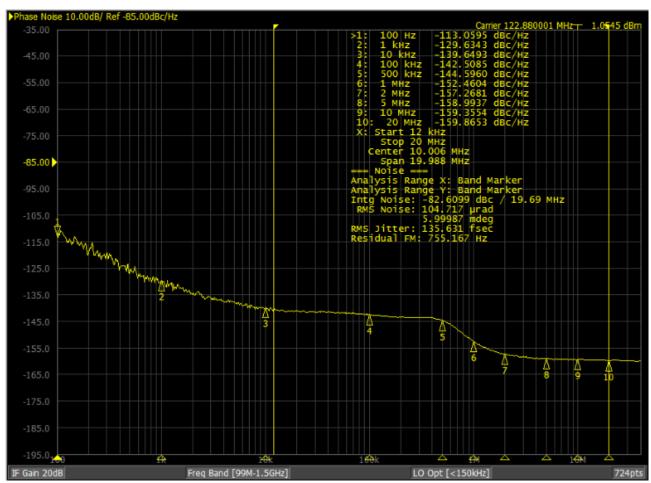

| Figure 4 Representative Close In Phase Noise Measurement                                             | 19 |

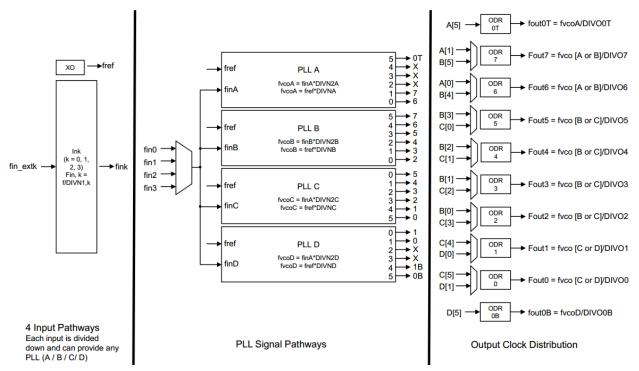

| Figure 5 Overall Architecture                                                                        | 22 |

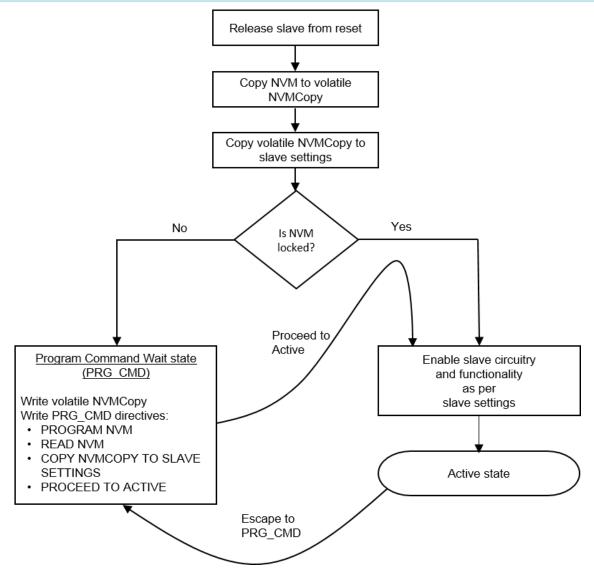

| Figure 6 Overall Hierarchy of Clocks                                                                 | 23 |

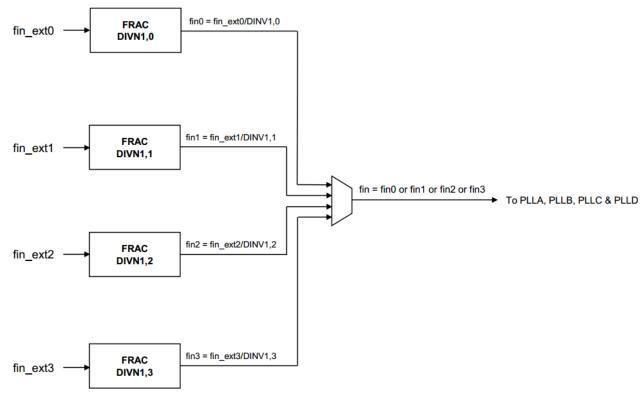

| Figure 7 Input Clock Distribution                                                                    | 24 |

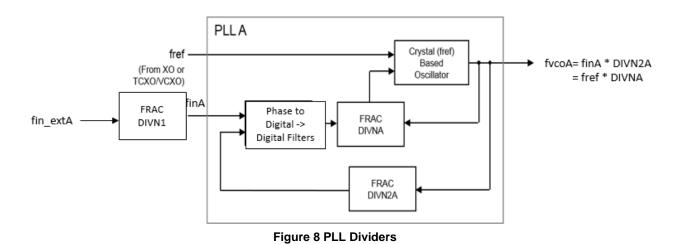

| Figure 8 PLL Dividers                                                                                | 24 |

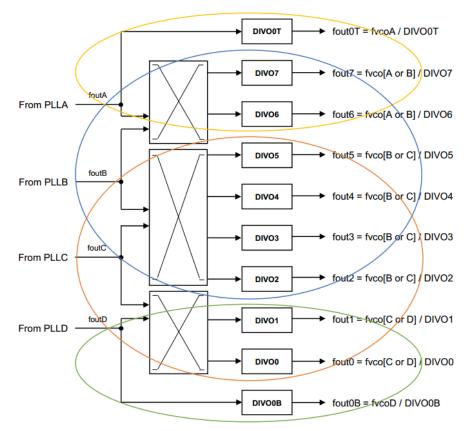

| Figure 9 Output Clock Distribution                                                                   | 25 |

| Figure 10 Master Memory Structure                                                                    | 26 |

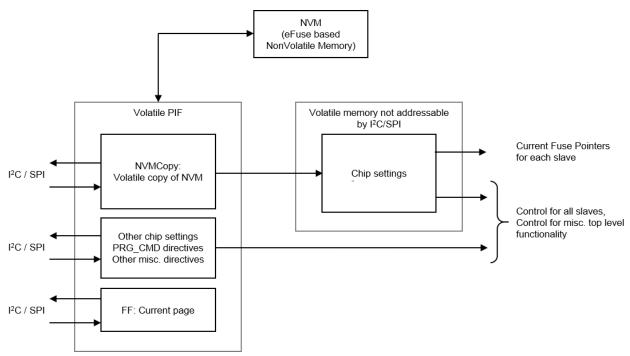

| Figure 11 Slave Memory Structure                                                                     | 27 |

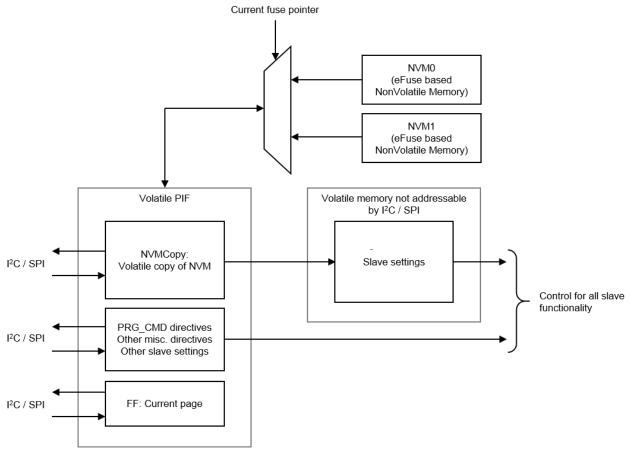

| Figure 12 Master Wake-up Finite State Machine                                                        | 28 |

| Figure 13 Slave Wake-up Finite State Machine                                                         | 29 |

| Figure 14 PLL Architecture                                                                           | 35 |

| Figure 15 Zero Delay Mode Set Up: PLLA in ZDB mode with OUT0T routed in to IN3 for the ZDB feedback. | 37 |

| Figure 16 I2C Timing Waveform                                                                        | 46 |

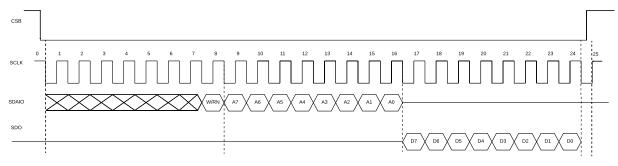

| Figure 17 SPI Timing Diagram                                                                         | 47 |

| Figure 18 SPI Write                                                                                  | 48 |

| Figure 19 SPI Read                                                                                   | 49 |

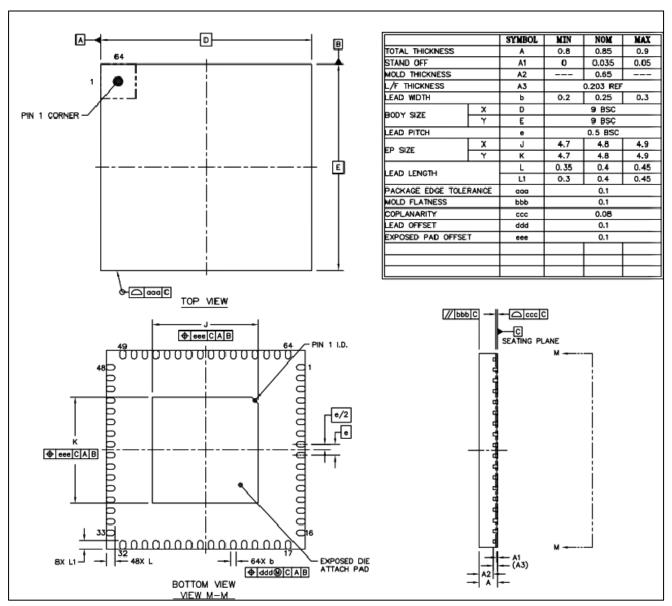

| Figure 20 64-QFN Package Dimensions                                                                  | 50 |

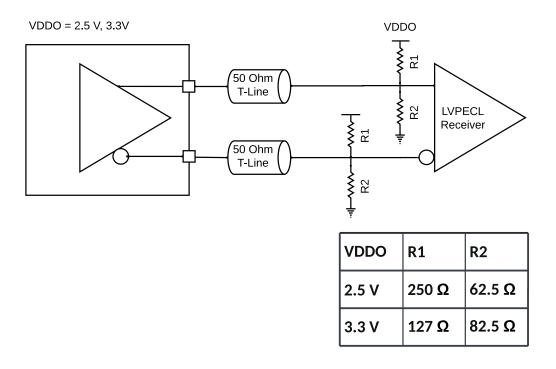

| Figure 21 LVPECL DC Termination to VDDO – 2V                                                         | 51 |

| Figure 22 LVPECL Alternate DC Termination: Thevenin Equivalent                                       | 51 |

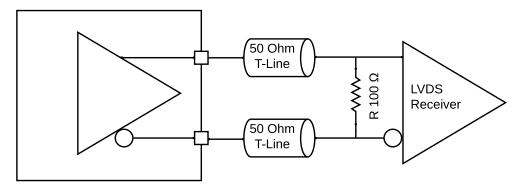

| Figure 23 DC Coupled LVDS Termination                                                                | 52 |

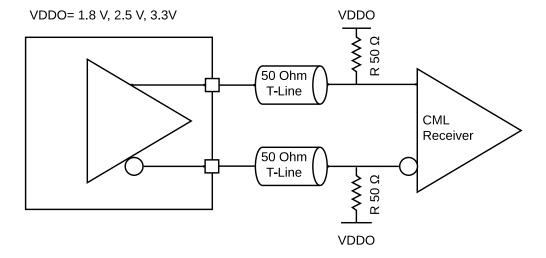

| Figure 24 DC Coupled CML                                                                             | 52 |

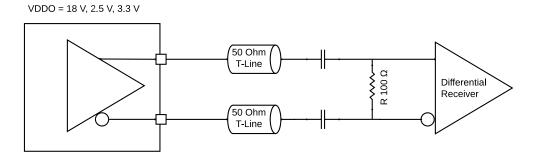

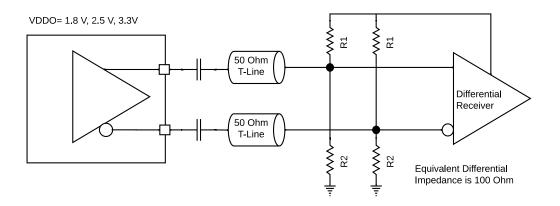

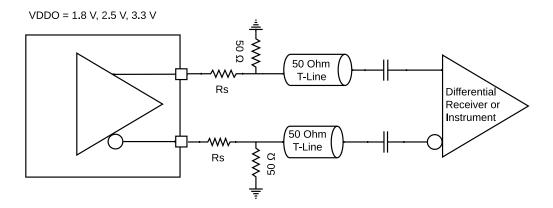

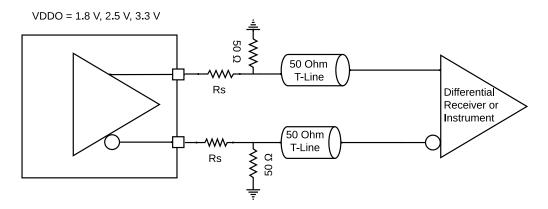

| Figure 25 AC Coupled Receiver side resistive Termination options                                     | 53 |

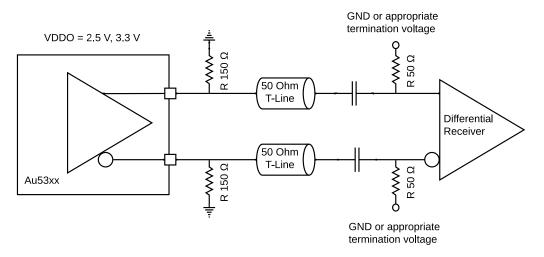

| Figure 26 Alternate AC Coupled LVPECL with DC coupled resistors on Chip side                         | 54 |

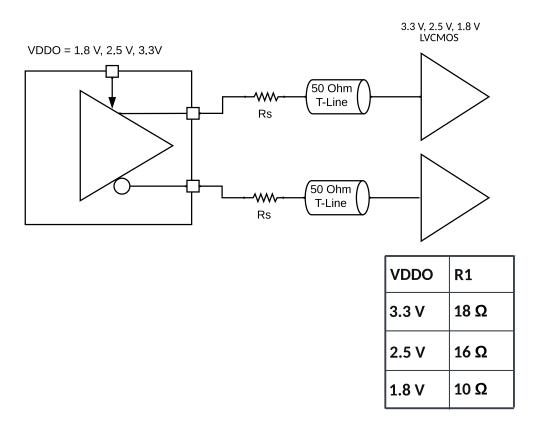

| Figure 27 DC Coupled LVCMOS                                                                          | 54 |

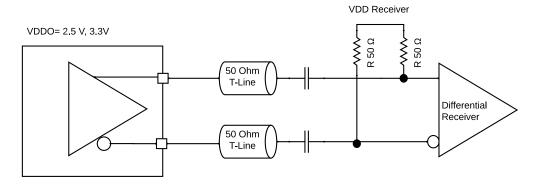

| Figure 28 HCSL AC Coupled Termination. Source Terminated 50 Ω                                        | 55 |

| Figure 29 HCSL DC Coupled Termination. Source Terminated 50 Ω                                        | 55 |

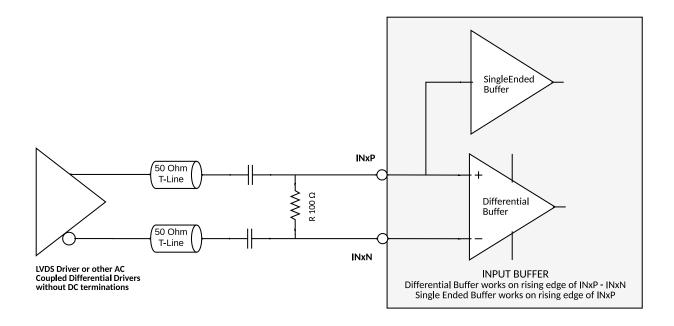

| Figure 30 AC Coupled Differential LVDS Input / AC Coupled Driver without DC Terminations             | 56 |

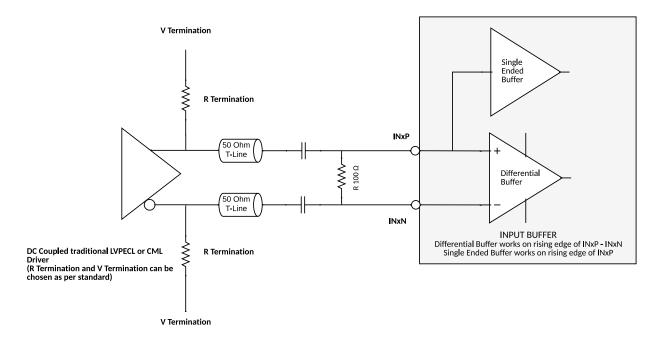

| Figure 31 AC Coupled Differential LVPECL or CML                                                      | 56 |

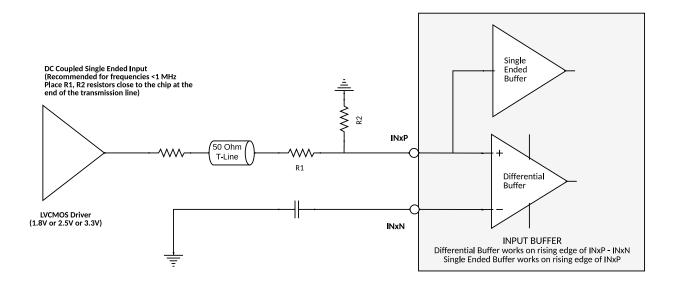

| Figure 32 DC Coupled Single Ended Driver                                                             | 57 |

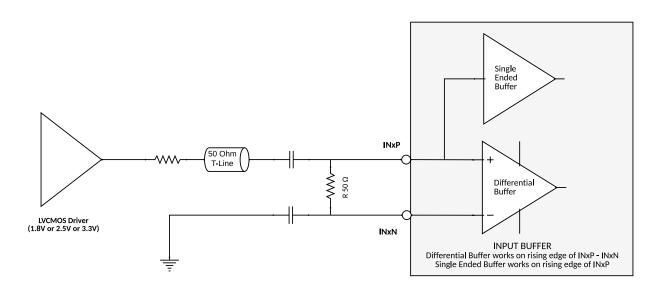

| Figure 33 AC Coupled Single Ended Driver with 50 Ohm Termination on receiver (chip) side             | 57 |

| Figure 34 AC Coupled Single Ended LVCMOS input without 50 Ohm Termination                            | 58 |

| Figure 35 Crystal Connection                                                                         | 59 |

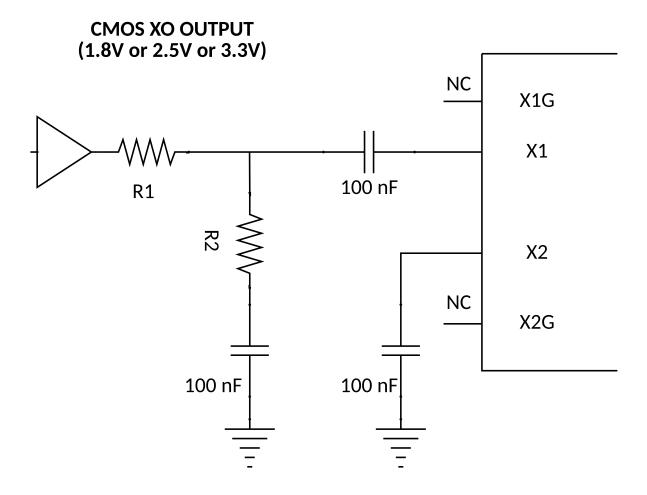

| Figure 36 CMOS XO Connection                                                                         | 60 |

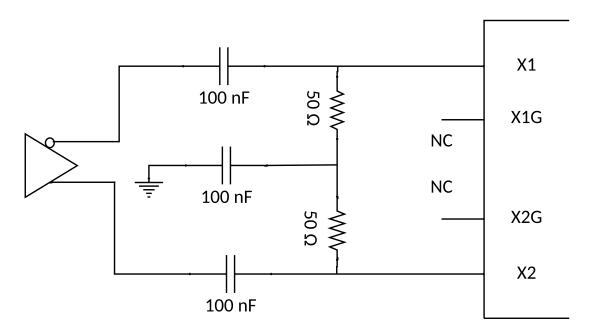

| Figure 37 Differential XO Connection                                                                 | 61 |

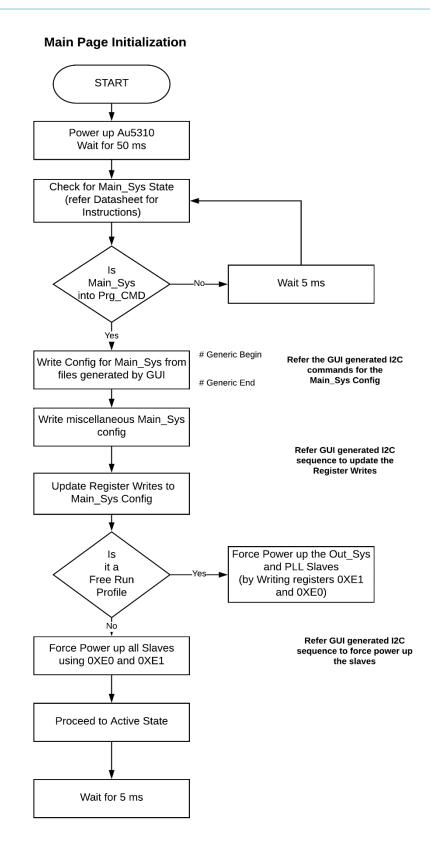

| Figure 38 STEP 1: Initialize the Main Page- Page 0.                                                  | 69 |

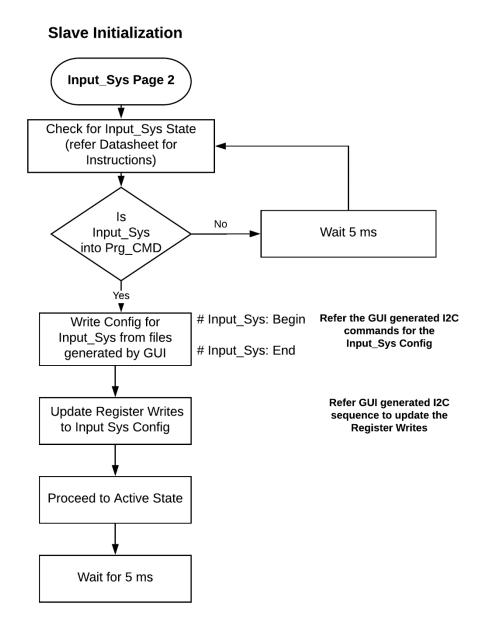

| Figure 39 STEP 2: Initialize the Input System Page- Page 2                                           | 70 |

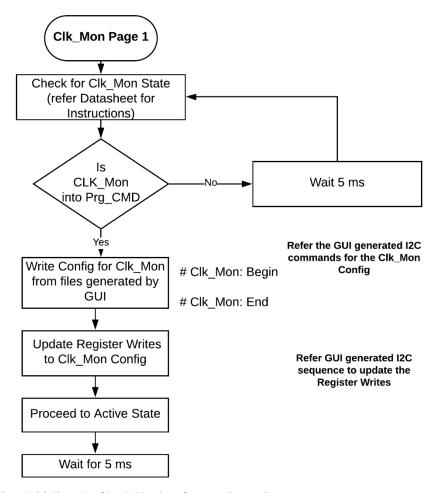

| Figure 40 STEP 3: Initialise the Clock Monitor System Page- Page 1                                   | 71 |

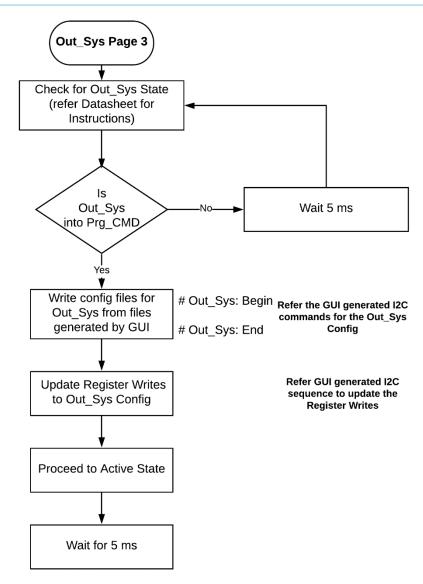

| Figure 41 STEP 4: Initialise the Output System Page- Page 3.                                         | 72 |

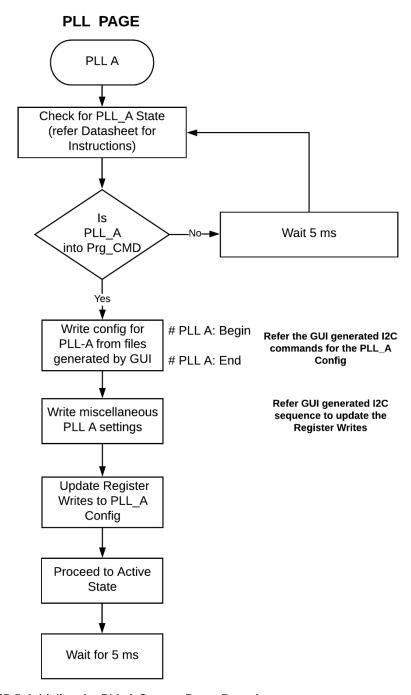

| Figure 42 STEP 5: Initialise the PLL A System Page- Page A                                           | 73 |

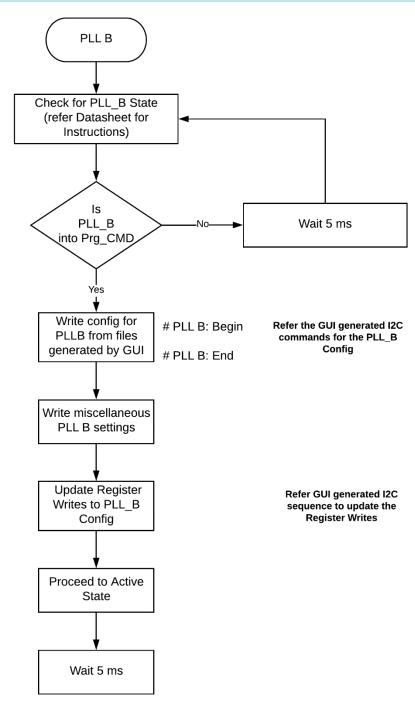

| Figure 43 STEP 6: Initialise the PLL B System Page- Page B                                           | 74 |

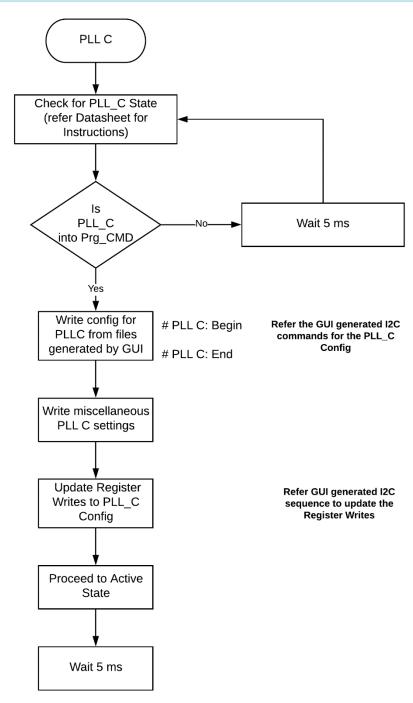

| Figure 44 STEP 7: Initialise the PLL C System Page- Page C.                                          | 75 |

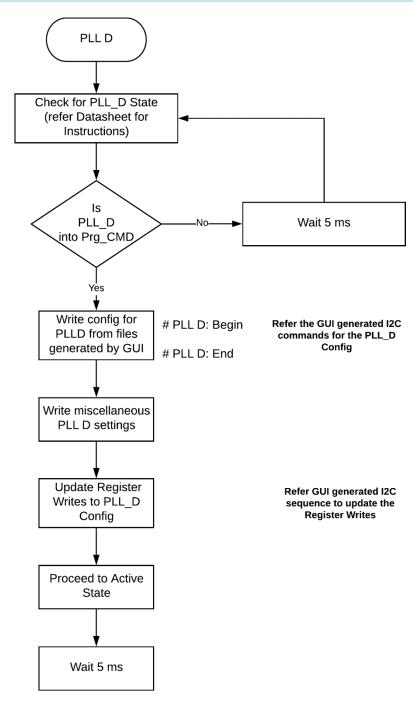

| Figure 45 STEP 8: Initialise the PLL D System Page- Page D                                           | 76 |

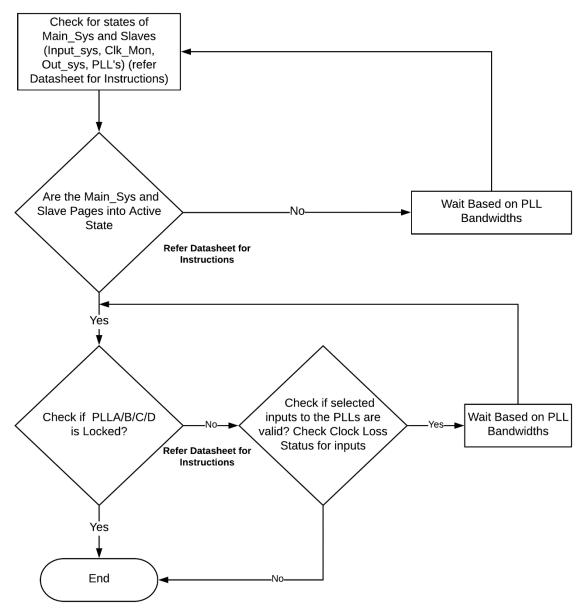

| Figure 46 Active State Confirmation  | 77 |

|--------------------------------------|----|

| i igaic to Active Otale Commitmation |    |

# 1 Pin Description

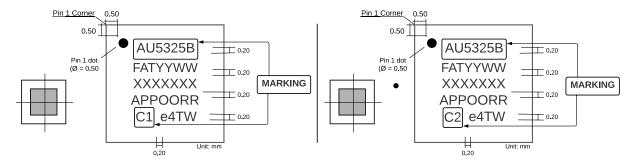

**Figure 2 Top View**

**Table 1 Pin Description**

| Pin Name | I/O Type | Pin No. | Function                                                                                                                                       | Comments                                                                                                                          |

|----------|----------|---------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| INOP     | Input    | 63      | True input for IN0 differential pair. Input for LVCMOS IN0 input. Need series external capacitor for differential input.                       |                                                                                                                                   |

| INON     | Input    | 64      | Complement input for IN0 differential pair. Ground with capacitor for LVCMOS IN0 input. Need series external capacitor for differential input. | IN0 / IN1 / IN2 / IN3 inputs can be                                                                                               |

| IN1P     | Input    | 1       | True input for IN1 differential pair. Input for LVCMOS IN1 input. Need series external capacitor for differential input.                       | used for output clock<br>synchronization. An active clock<br>and three spare clocks are chosen<br>such that the same choice holds |

| IN1N     | Input    | 2       | Complement input for IN1 differential pair. Ground with capacitor for LVCMOS IN1 input. Need series external capacitor for differential input. | for all PLLs.                                                                                                                     |

| IN2P     | Input    | 14      | True input for IN2 differential pair. Input for LVCMOS IN2 input. Need series external capacitor for differential input.                       |                                                                                                                                   |

| Pin Name | I/O Type | Pin No. | Function                                                                                                                                       | Comments                                    |

|----------|----------|---------|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| IN2N     | Input    | 15      | Complement input for IN2 differential pair. Ground with capacitor for LVCMOS IN2 input. Need series external capacitor for differential input. |                                             |

| IN3P     | Input    | 61      | True input for IN3 differential pair. Input for LVCMOS IN3 input. Need series external capacitor for differential input.                       |                                             |

| IN3N     | Input    | 62      | Complement input for IN3 differential pair. Ground with capacitor for LVCMOS IN3 input. Need series external capacitor for differential input. |                                             |

| GND      | Power    | EPAD    | Electrical and Package Ground                                                                                                                  | Exposed Ground on the bottom E-PAD          |

| OUT0P    | Output   | 28      | Output 0 True Output or Output 0 LVCMOS.                                                                                                       |                                             |

| OUTON    | Output   | 27      | Output 0 Complement Output or Output 0 LVCMOS.                                                                                                 |                                             |

| OUT1P    | Output   | 31      | Output 1 True Output or Output 1 LVCMOS.                                                                                                       |                                             |

| OUT1N    | Output   | 30      | Output 1 Complement Output or Output 1 LVCMOS.                                                                                                 |                                             |

| OUT2P    | Output   | 35      | Output 2 True Output or Output 2 LVCMOS.                                                                                                       |                                             |

| OUT2N    | Output   | 34      | Output 2 Complement Output or Output 2 LVCMOS.                                                                                                 |                                             |

| OUT3P    | Output   | 38      | Output 3 True Output or Output 3 LVCMOS.                                                                                                       |                                             |

| OUT3N    | Output   | 37      | Output 3 Complement Output or Output 3 LVCMOS.                                                                                                 |                                             |

| OUT4P    | Output   | 42      | Output 4 True Output or Output 4 LVCMOS.                                                                                                       |                                             |

| OUT4N    | Output   | 41      | Output 4 Complement Output or Output 4 LVCMOS.                                                                                                 | LVPECL, LVDS, HCSL, CML and LVCMOS support. |

| OUT5P    | Output   | 45      | Output 5 True Output or Output 5 LVCMOS.                                                                                                       |                                             |

| OUT5N    | Output   | 44      | Output 5 Complement Output or Output 5 LVCMOS.                                                                                                 |                                             |

| OUT6P    | Output   | 51      | Output 6 True Output or Output 6 LVCMOS.                                                                                                       |                                             |

| OUT6N    | Output   | 50      | Output 6 Complement Output or Output 6 LVCMOS.                                                                                                 |                                             |

| OUT7P    | Output   | 54      | Output 7 True Output or Output 7 LVCMOS.                                                                                                       |                                             |

| OUT7N    | Output   | 53      | Output 7 Complement Output or Output 7 LVCMOS.                                                                                                 |                                             |

| OUT0BP   | Output   | 24      | Output 0B True Output or Output 0B LVCMOS.                                                                                                     |                                             |

| OUT0BN   | Output   | 23      | Output 0B Complement Output or Output 0B LVCMOS.                                                                                               |                                             |

| ОПТОТР   | Output   | 59      | Output 0T True Output or Output 0T LVCMOS.                                                                                                     |                                             |

| OUT0TN   | Output   | 58      | Output 0T Complement Output or Output 0T LVCMOS.                                                                                               |                                             |

| Pin Name  | I/O Type          | Pin No. | Function                                                                                                                                                           | Comments                                                                      |

|-----------|-------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| VDDIN     | Power             | 13      | Power Supply Voltage pin                                                                                                                                           | Decoupling capacitor close to supply pin required.                            |

| VDD       | Power             | 46,60   | Power Supply Voltage pin                                                                                                                                           | Multiple Supply Pins, Decoupling capacitor close to each supply pin required. |

| IN_SEL0   | Input             | 3       | Input Clock Selection for Manual                                                                                                                                   |                                                                               |

| IN_SEL1   | Input             | 4       | selection of active clock. Can be left floating or pulled down to GND if not used.                                                                                 |                                                                               |

| FLEXIO3   | Output            | 5       | Flexible Status GPIO. Can be left floating or pulled down to GND if not used.                                                                                      |                                                                               |

| RSTB      | Input             | 6       | Active low reset internally pulled up to VDDIO; Pull Up Resistor to VDDIO of fixed value (25 K $\Omega$ ). Can be left floating or pulled up to VDDIO if not used. | Active low signal performs a complete reset of the part                       |

| OEb       | Input             | 11      | Used to disable (when 1) all the output clocks. Can be left floating or pulled down to GND if not used.                                                            |                                                                               |

| INTRb     | Output            | 12      | Active low indicator of programmable sticky notifies. Can be left floating if not used.                                                                            |                                                                               |

| SCLK      | Input             | 16      | I2C Serial Interface Clock or SPI Clock Input. Pull Up Resistor to VDDIO of fixed value (25 $K\Omega$ ).                                                           |                                                                               |

| SDO       | Output            | 17      | Serial Data Output (SPI Interface). In I2C mode this is the A1 address pin (see I2C section).                                                                      |                                                                               |

| SDAIO     | Input /<br>Output | 18      | I2C Serial Interface Data (SDA) / SPI Input data (SDI).                                                                                                            |                                                                               |

| CSB       | Input             | 19      | Chip Select for the SPI Interface.<br>In I2C mode this is the A0 address pin (see I2C section).                                                                    |                                                                               |

| FDEC      | Input/Output      | 25      | DCO Decrement. Can be left floating or pulled down to GND if not used.                                                                                             |                                                                               |

| I2C1_SPI0 | Input             | 39      | Choose between SPI(0) and I2C(1) interface being used.                                                                                                             |                                                                               |

| LOLb      | Output            | 47      | Loss of Lock Indicator (NOR value of all PLLs' LOL active high indicators comes out on the LOLb pin). Can be left floating if not used.                            |                                                                               |

| FINC      | Input/Output      | 48      | DCO Increment. Can be left floating or pulled down to GND if not used.                                                                                             |                                                                               |

| FLEXIO14  | Input/Output      | 55      | Flexible Outputs can be used for                                                                                                                                   |                                                                               |

| FLEXIO15  | Input/Output      | 56      | programmable status monitoring (Refer AN53001 for more information). Can be left floating or pulled down to GND if not used.                                       |                                                                               |

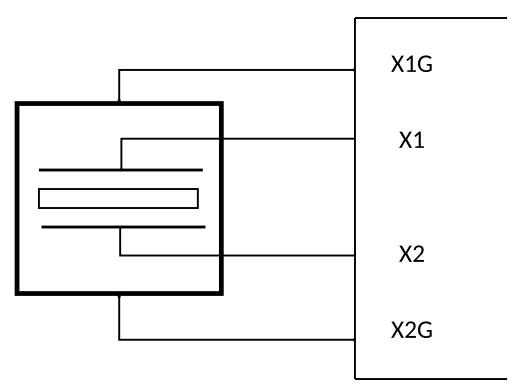

| {X1, X1G} | Input/Output      | 8,7     | Crystal X1 Pin and accompanying ground pin                                                                                                                         | {X1G, X2G} land on a floating                                                 |

| {X2, X2G} | Input/Output      | 9,10    | Crystal X2 Pin and accompanying ground pin                                                                                                                         | island on the PCB                                                             |

| Pin Name | I/O Type      | Pin No.      | Function                                          | Comments                           |

|----------|---------------|--------------|---------------------------------------------------|------------------------------------|

| VDDO0    | Power         | 26           | Output Power Supply for Bank 0 outputs            |                                    |

| VDDO1    | Power         | 29           | Output Power Supply for Bank 1 outputs            |                                    |

| VDDO2    | Power         | 33           | Output Power Supply for Bank 2 outputs            |                                    |

| VDDO3    | Power         | 36           | Output Power Supply for Bank 3 outputs            |                                    |

| VDDO4    | Power         | 40           | Output Power Supply for Bank 4 outputs            | Decoupling capacitor close to each |

| VDDO5    | DDO5 Power 43 | 43           | Output Power Supply for Bank 5 outputs            | supply pin required.               |

| VDDO6    | DO6 Power 49  |              | Output Power Supply for Bank 6 outputs            |                                    |

| VDDO7    | Power         | 52           | Output Power Supply for Bank 7 outputs            |                                    |

| VDDO0T   | Power         | 57           | Output Power Supply for Bank 8 outputs            |                                    |

| VDDO0B   | Power         | 22           | Output Power Supply for Bank 9 outputs            |                                    |

| NC       | No Connect    | 20,21,<br>32 | No connect. This pin is not connected to the die. |                                    |

#### Notes:

- 1. VDDIO is the voltage used for all the status GPIOs and the serial interface. The default voltage for VDDIO can be chosen as either VDDIN or VDD through the programmable GUI (Enabled only on selected GUI variants).

- 2. Configure VDDIO as VDD and VDDIN using 0x23[7] on Page0 as per below table:

| Variant   | Default VDDIO Power Up | VDDIO=VDD                  | VDDIO=VDDIN                |

|-----------|------------------------|----------------------------|----------------------------|

| AU5325BC1 | VDD                    | 0x23[7]=0, Page0 (Default) | Not Supported              |

| AU5325BC2 | VDDIN                  | Not Supported              | 0x23[7]=1, Page0 (Default) |

- 3. All digital input/output GPIOs (FLEXIOs) have an on-chip 25 kΩ pull down resistor to ePAD ground (unless mentioned otherwise)and can be left unconnected if not used.

- 4. The I2C1\_SPI0 pad has a an on-chip 25 kΩ pull up resistor to indicate default mode of communication as I2C unless this pin is pulled down on the board to indicate the SPI mode.

- 5. In I2C mode, the serial data and clock have an on-chip 25 k $\Omega$  pull up resistor to VDDIO.

- 6. The RSTB pin has an on-chip 25 kΩ pull up resistor to VDDIO. Writing 0xFE[0] to 1 with delay addition of 10ms has the same effect as the pulling RSTB pin to GND for chip reset.

- 7. SDO and CSB pins are used to set the I2C default address as 0x69 when floating since SDO and CSB has 25k pull down and pull up to GND and VDDIN respectively. Otherwise the I2C address can be changed as 11010{SDO},{CSB} by forcing the SDO and CSB externally to VDDIN or GND accordingly.

- a. The chip can be reset from the register map by writing address 0xFE as 0x01 using the current I2C address.

- b. To disable reset from register map by writing 0xFE register as 0x00, Address needs to be 0b11010{SDO}{CSB}, 5 MSB address bits are 11010, LSB 2 bits are the state of SDO and CSB pins. If these pins are floating, use 0x69 as the address. At all other times default slave address chosen for the part can be used.

## 2 Electrical Characteristics

**Table 2 Absolute Maximum Ratings**

| Description                | Conditions           | Symbol             | Min   | Тур | Max   | Units |

|----------------------------|----------------------|--------------------|-------|-----|-------|-------|

| Core supply voltage,       |                      | V <sub>DDIN</sub>  | -0.5  |     | +3.63 | V     |

| Analog Input               |                      | V DDIN             | -0.5  |     | +3.03 | V     |

| Core supply voltage, PLL   |                      | V <sub>DD</sub>    | -0.5  |     | +3.63 |       |

| Output bank supply         |                      | V <sub>DDO</sub>   | -0.5  |     | +3.63 | V     |

| voltage                    |                      | V DDO              | -0.5  |     | +3.03 | V     |

| Input voltage, All Inputs  | Relative to GND      | VIN                | -0.5  |     | +3.63 | V     |

| XO Inputs <sup>3</sup>     | Relative to GND      | V <sub>XO</sub>    | -0.5  |     | +1.4  | V     |

| I2C Bus input voltage      | SCLK, SDAT pins      | V <sub>INI2C</sub> | -0.5  |     | +3.63 | V     |

| SPI Bus input voltage      |                      | VINSPI             | -0.5  |     | +3.63 | V     |

| Storage temperature        | Non-functional, Non- | Ts                 | -55   |     | +150  | °C    |

| Storage temperature        | Condensing           | 15                 | -55   |     | 1100  |       |

| Programming                |                      | TPROG              | +25   |     | +85   | °C    |

| Temperature                |                      | TPROG              | 720   |     | +03   | O     |

| Maximum Junction           |                      |                    |       |     |       |       |

| Temperature in             |                      | Тјст               |       |     | +125  | °C    |

| Operation                  |                      |                    |       |     |       |       |

| Programming Voltage        |                      |                    |       |     |       |       |

| (for Programming the       |                      | $V_{PROG}$         | 2.375 | 2.5 | 2.625 | V     |

| OTP Fuse Memory).          |                      |                    |       |     |       |       |

| ESD (human body            | JESD22A-114          | ESDHBM             |       |     | 2000  | V     |

| model)                     | JLGD22A-114          | LODHRM             |       |     | 2000  | v     |

| Latchup                    | JEDEC JESD78D        | LU                 |       |     | 100   | mA    |

| Moisture Sensitivity Level | 64-QFN               | MSL                |       | 3   |       | •     |

#### Notes:

- 1. Exceeding maximum ratings may shorten the useful life of the device.

- 2. Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or at any other conditions beyond those indicated under the DC Electrical Characteristics is not implied. Exposure to Absolute-Maximum-Rated conditions for extended periods may affect device reliability or cause permanent device damage.

- 3. Refer to AN53012 for the additional information on the absolute minimum and maximum voltage on XO Inputs before and after the chip power up.

Table 3 Operating Temperatures, Thermal Characteristics and Environmental Compliance

| Description                               | Conditions    | Symbol        | Min  | Тур  | Max  | Units |

|-------------------------------------------|---------------|---------------|------|------|------|-------|

| Ambient temperature                       |               | TA            | -40  | _    | +85  | °C    |

| Junction temperature                      |               | TJ            |      |      | +125 | °C    |

| IB ::                                     | Still Air     | $\theta_{JA}$ |      | 25.5 |      | °C/W  |

| Thermal Resistance Junction to Ambient    | Air Flow 1m/s |               | 20.8 |      |      | °C/W  |

| Sundion to Ambient                        | Air Flow 2m/s |               |      |      | °C/W |       |

| Thermal Resistance Junction to Case       |               | θυς           |      | 8.70 |      | °C/W  |

| Thermal Resistance Junction to Board      |               | θЈВ           |      | 7.07 |      | °C/W  |

| Thermal Resistance Junction to Top Center |               | ψυτ           |      | 0.2  |      | °C/W  |

| Moisture Sensitivity Level                | 64-QFN        | MSL           |      | 3    |      | _     |

## **Table 4 DC Electrical Characteristics**

| Description                                                   | Conditions        | Symbol            | Min  | Тур  | Max  | Units |

|---------------------------------------------------------------|-------------------|-------------------|------|------|------|-------|

| Supply voltage, Analog<br>Input Pathways and<br>XTAL Pathways | 3.3 V range: ±10% | V <sub>DDIN</sub> | 2.97 | 3.3  | 3.63 | V     |

| Supply voltage, PLL                                           | 1.8 V range: ±5%  | $V_{DD}$          | 1.71 | 1.80 | 1.89 | V     |

| Description                                                 | Conditions                                                                                                      | Symbol                          | Min   | Тур  | Max   | Units |

|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|---------------------------------|-------|------|-------|-------|

|                                                             | 2.5 V range: ±5 %                                                                                               |                                 | 2.375 | 2.50 | 2.625 | V     |

|                                                             | 3.3 V range: ±10%                                                                                               |                                 | 2.97  | 3.3  | 3.63  | V     |

| 0 1 1/1 1/1 0 1 1                                           | 1.8 V range: ±5%                                                                                                |                                 | 1.71  | 1.80 | 1.89  | V     |

| Supply Voltage, Output Drivers                              | 2.5 V range: ±5%                                                                                                | V <sub>DDO</sub>                | 2.375 | 2.50 | 2.625 | V     |

| Dilvers                                                     | 3.3 V range: ±10%                                                                                               |                                 | 2.97  | 3.3  | 3.63  | V     |

|                                                             | 1.8 V range: ±5%                                                                                                |                                 | 1.71  | 1.80 | 1.89  | V     |

| Programmable Status Supply for selected IOs                 | 2.5 V range: ±5%                                                                                                | V <sub>DDS</sub>                | 2.375 | 2.50 | 2.625 | V     |

| Cupply for delected fee                                     | 3.3 V range: ±10%                                                                                               |                                 | 2.97  | 3.3  | 3.63  | V     |

| For VDDIN = 3.3 V, VDD                                      | = 1.8 V                                                                                                         |                                 |       |      |       |       |

| Total Power Dissipation<br>(2.5V LVDS Outputs @<br>156.25M) | 4 PLLs, 10 Outputs<br>(4 Independent<br>Fractional Translations)                                                | Pd                              |       | 1054 | 1265  | mW    |

| - ,                                                         | 1 PLL, 2 Outputs                                                                                                |                                 |       | 250  | 300   | mW    |

| Supply Current, VDDIN                                       | All Four Inputs assumed to be enabled                                                                           | I <sub>DDIN<sup>[1]</sup></sub> |       | 18   | 21.6  | mA    |

| Supply Current, VDD                                         | All Four PLLs and All<br>10 Outputs enabled<br>(Maximum current<br>mode)                                        | lod                             |       | 340  | 408   | mA    |

|                                                             | LVPECL, output pair terminated 50 $\Omega$ to V <sub>TT</sub> (VDDO – 2 V).                                     |                                 |       | 40   | 48    | mA    |

| Power supply current,<br>VDDO                               | LVPECL2, output pair terminated 50 $\Omega$ to V <sub>TT</sub> (VDDO – 2 V) or 0 V without common mode current. | I <sub>DDO</sub> [2,3,4,5,6]    |       | 28   | 36    | mA    |

| Power supply current,<br>VDDO                               | CML, output pair terminated 50 $\Omega$ to VDDO                                                                 | I <sub>DDO</sub> [2,3,4,5,6,7]  |       | 20   | 24    | mA    |

| Power supply current, VDDO                                  | HCSL, output pair with HCSL termination                                                                         | IDDO <sup>[2,3,4,5,6,7]</sup>   |       | 27   | 36    | mA    |

| Power supply current, VDDO                                  | LVDS, output pair terminated with an AC or DC Coupled diff $100~\Omega$                                         | I <sub>DDO</sub> [2,3,4,5,6,7]  |       | 16   | 19.2  | mA    |

| Power supply current, VDDO                                  | LVDS Boost, output pair terminated with an AC or DC Coupled diff $100~\Omega$                                   | IDDO <sup>[2,3,4,5,6,7]</sup>   |       | 20   | 24    | mA    |

| Power supply current,<br>VDDO                               | LVCMOS, 250 MHz,<br>2.5 V output, 5-pF load                                                                     | IDDO <sup>[2,3,4,5,6,7]</sup>   |       | 15   | 18    | mA    |

#### Notes:

- 1. VDDIN = 3.3 V and VDD = 1.8V/2.5V/3.3V is the recommended supply combination for Au5325. Additional current consumption of 3 mA for a third overtone crystal instead of a fundamental mode crystal.

- 2. LVPECL and LVDS Boost standards are supported for VDDO = {2.5 V, 3.3 V}. LVPECL2, HCSL, CML and LVDS standards are supported for VDDO = {1.8 V, 2.5 V, 3.3 V}.

- 3. LVPECL mode provides 6mA of common mode current on each output. LVPECL2 mode does not provide this common mode current.

- 4. A 50  $\Omega$  Termination resistor with a DC bias of VDDO 2 V for LVPECL standards is supported for VDDO = {2.5 V, 3.3 V}.

- 5. IDDOx Output driver supply current specified for one output driver in the table. This includes current in each of the output module that includes output dividers, drivers and clock distributions.

- 6. The LVDS Boost Mode and the LVDS Mode can be used for AC Coupled output terminations. LVDS Boost provides an LVPECL like swing with an AC Coupled 100 Ω Differential termination.

- 7. Refer to Output Termination Information in the data sheet for the descipription of the various terminations that are supported.

- 8. For efuse programming in AU5325, VDD alongwith VDDIN can be set to 2.5 V and has no reliability concerns. Refer to Programming the Primary E-Fuse section for VDD/VDDIN voltage information for efuse programming.

### **Table 5 Input Clock Characteristics**

| Parameter                                                               | Conditions                                     | Symbol                      | Min              | Тур                | Max    | Unit      |

|-------------------------------------------------------------------------|------------------------------------------------|-----------------------------|------------------|--------------------|--------|-----------|

| Standard Input Buffer with                                              | Differential or Single-Ended                   | — AC-couple                 | d (INO/INO, IN1/ | /IN1, IN2/IN2, IN: | 3/IN3) |           |

|                                                                         | Differential                                   |                             | 0.008            | _                  | 2100   | MHz       |

| Input Frequency Range                                                   | All Single-ended signals (including LVCMOS)    | f <sub>IN</sub>             | 0.008            | _                  | 250    | MHz       |

| Voltage Swing (Differential                                             | AC-coupled f <sub>IN</sub> < 400 MHz           |                             | 100              |                    |        | mV        |

| Amplitude Peak or Single<br>Ended Peak to Peak for the                  | 400 MHz < AC-coupled f <sub>IN</sub> < 750 MHz | -                           | 225              | _                  |        | mV        |

| differential signal) [1]                                                | 750 MHz < AC-coupled fIN < 2100 MHz            | V <sub>IN</sub>             | 350              | _                  |        | mV        |

| Single Ended AC Coupled Inputs (Single Ended Peak to Peak Input) [1][4] | AC-Coupled f <sub>IN</sub> < 250 MHz           |                             | 500              | -                  | 3600   | mV        |

| Slew Rate [2,3]                                                         |                                                | SR                          | 400              | _                  | _      | V/µs      |

| Duty Cycle                                                              |                                                | DC                          | 40               | _                  | 60     | %         |

| Input Capacitance                                                       |                                                | C <sub>IN</sub>             | _                | 0.3                | _      | pF        |

| Input Resistance                                                        | AC Coupled SE                                  | R <sub>IN</sub>             | _                | 15                 | _      | kΩ        |

|                                                                         | Differential                                   |                             | _                | 10                 | _      | kΩ        |

| Pulsed CMOS Input Buffe                                                 | r — DC-coupled (IN0, IN1, IN                   | 2, IN3) <sup>[3]</sup>      |                  |                    |        | •         |

| Input Frequency                                                         |                                                | f <sub>IN_PULSED_CMOS</sub> | 0.008            | _                  | 250    | MHz       |

| Inner Maltana                                                           |                                                | V <sub>IL</sub>             | -0.2             | _                  | 0.4    | V         |

| Input Voltage                                                           |                                                | V <sub>IH</sub>             | 0.8              | _                  | _      | V         |

| Slew Rate [2,3]                                                         |                                                | SR                          | 400              | _                  | _      | V/µs      |

| Duty Cycle                                                              |                                                | DC                          | 40               | _                  | 60     | %         |

| Minimum Pulse Width                                                     | Pulse Input                                    | PW                          | 1.6              | _                  | _      | ns        |

| Input Resistance                                                        |                                                | R <sub>IN</sub>             | _                | 30                 | _      | kΩ        |

| Reference Clock (Applied                                                | to X1), Can be external XO, 1                  | CXO or OCXO                 | 1                |                    |        |           |

| Reference Clock                                                         | Range for best jitter                          | _                           | 48               | -                  | 160    | MHz       |

| Frequency                                                               | Overall supported range                        | F <sub>IN_REF</sub>         | 37.5             | -                  | 160    | MHz       |

| Innut Voltage Codes                                                     | Single Ended peak to peak                      | V <sub>IN_SE</sub>          | 365              | -                  | 2000   | mVpp_se   |

| Input Voltage Swing                                                     | Differential peak to peak                      | $V_{IN\_DIFF}$              | 365              | -                  | 2500   | mVpp_diff |

| Slew rate                                                               |                                                | SR                          | 400              | -                  | -      | V/us      |

| Duty Cycle                                                              |                                                | DC                          | 40               | -                  | 60     | %         |

#### Notes:

- 1. AC Coupled input assumed with series capacitance for differential inputs or single ended AC Coupled inputs. Swing requirement at device pins

- 2. Resistor termination for differential input followed by series capacitors for each of true and complement differential input connecting to the device pins.

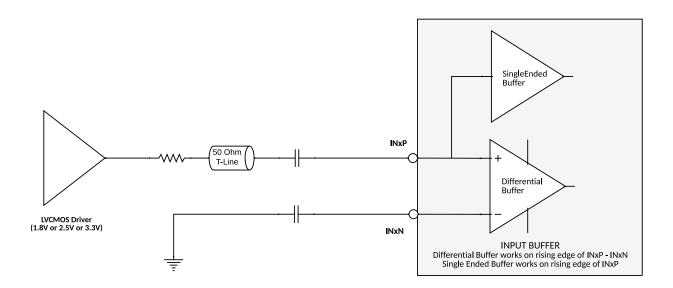

- 3. LVCMOS single ended is direct coupled on the true input. Connect complement input to ground with a 100nF capacitor.

- 4. Single Ended AC coupled Input Swing requirement (Single Ended Peak to Peak Input) [1][4] is for optimal noise performance.

### **Table 6 Serial and Clock Input**

| Parameter           | Condition  | Symbol          | Min                       | Тур | Max                       | Unit |

|---------------------|------------|-----------------|---------------------------|-----|---------------------------|------|

| land Maltana        |            | VIL             | _                         | _   | $0.3 \times V_{DDIO}^{1}$ | V    |

| Input Voltage       |            | VIH             | $0.7 \times V_{DDIO}^{1}$ | _   | _                         | V    |

| Input Capacitance   |            | C <sub>IN</sub> | _                         | 1   | _                         | pF   |

| Input Resistance    |            | R <sub>IN</sub> | _                         | 25  | _                         | kΩ   |

| Minimum Pulse Width | FINC, FDEC | PW              | 100                       | _   | _                         | ns   |

| Update Rate         | FINC, FDEC | Fur             | _                         | _   | 1                         | μs   |

#### Notes:

1. VDDIO is the voltage used for all the status GPIOs and the serial interface. The default voltage for VDDIO can be chosen as either VDDIN or VDD with a hard coded eFuse based selection.

## **Table 7 Output Serial and Status Pin**

| Parameter             | Test Condition          | Symbol | Min                      | Тур | Max                      | Unit |  |  |

|-----------------------|-------------------------|--------|--------------------------|-----|--------------------------|------|--|--|

| All VDDIO based GPIOs |                         |        |                          |     |                          |      |  |  |

| Outrot Valta aa       | I <sub>OH</sub> = -2 mA | Vон    | V <sub>DDIO</sub> x 0.75 | _   | _                        | V    |  |  |

| Output Voltage        | I <sub>OL</sub> = 2 mA  | VoL    | _                        |     | V <sub>DDIO</sub> x 0.25 | V    |  |  |

| All VDD based GPIOs   |                         |        |                          |     |                          |      |  |  |

| Outrant Maltage       | I <sub>OH</sub> = -2 mA | Vон    | V <sub>DDS</sub> x 0.75  | _   | _                        | V    |  |  |

| Output Voltage        | I <sub>OL</sub> = 2 mA  | VoL    | _                        |     | V <sub>DDS</sub> x 0.25  | V    |  |  |

### Notes:

## **Table 8 Output Clock Characteristics**

| Description                                                                  | Conditions                                                                                                               | Symbol                                | Min   | Тур   | Max   | Units |

|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-------|-------|-------|-------|

| Differential output frequency                                                | LVPECL, CML, LVDS outputs                                                                                                | F <sub>OUT,DIFF</sub> [1]             | 1     |       | 2100M | Hz    |

| Differential output frequency                                                | HCSL outputs                                                                                                             | F <sub>OUT,DIFFH</sub> <sup>[1]</sup> | 1     |       | 700 M | Hz    |

| Single ended output frequency                                                | LVCMOS outputs                                                                                                           | F <sub>OUN,SE</sub> <sup>[1]</sup>    | 1     |       | 250 M | Hz    |

| PLL loop bandwidth                                                           | Programmable                                                                                                             | F <sub>BW</sub>                       | 0.001 |       | 4000  | Hz    |

| Jitter peaking                                                               | Meets SONET Jitter<br>Peaking requirements<br>in closed loop                                                             | J <sub>PEAK</sub>                     |       |       | 0.1   | dB    |

| Time delay before the Historical average for output Frequency is considered. | Programmable in register map                                                                                             | H <sub>DELAY</sub> [2,3]              | 0.035 | 0.5   | 35    | s     |

| Length of time for<br>which the Average of<br>the frequency is<br>considered | Programmable in register map                                                                                             | H <sub>AVG</sub> <sup>[2,3]</sup>     | 0.07  | 1     | 70    | S     |

| Power Supply to I2C or<br>SPI interface ready                                | No I2C transaction valid till 10ms after all power supplies are ramped to 90% of final value.                            | T <sub>START</sub>                    |       |       | 10    | ms    |

| With Speed-Up mode enabled                                                   | Speed-up mode is programmable. This is a Typical number. Actual wake up time depends on fast lock and normal BW settings | T <sub>LOCK</sub> <sup>[4]</sup>      |       | 300   |       | ms    |

| DCO Mode Frequency<br>Step<br>Resolution                                     | Frequency Increment or Decrement resolution. This is controlled through the register map.                                | F <sub>RES,DCO</sub> <sup>[5]</sup>   |       | 0.005 |       | ppb   |

| Resolution for output delay                                                  | Programmable per<br>output clock with this<br>resolution for a total<br>delay of ±7.5 ns                                 | T <sub>RES</sub> <sup>[6]</sup>       |       | 35    |       | ps    |

| Maximum Phase Hit                                                            | Default Hitless Switching Mode (no phase propagation)                                                                    | T <sub>MAX</sub> <sup>[7]</sup>       | -50   |       | 50    | ps    |

| Uncertainty in Input to<br>Output Delay                                      | Maximum variation in<br>the static delay from<br>input to output clock<br>between repeated<br>power ups of the chip      | $\Delta T_{DELAY}$                    | -175  |       | 175   | ps    |

| Pull Range                                                                   |                                                                                                                          | ω <sub>P</sub>                        |       | 500   |       | ppm   |

<sup>1.</sup> VDDIO is the voltage used for all the status GPIOs and the serial interface. The default voltage for VDDIO can be chosen as either VDDIN or VDD with a hard coded eFuse based selection.

| Description                                | Conditions               | Symbol                                 | Min | Тур | Max | Units |

|--------------------------------------------|--------------------------|----------------------------------------|-----|-----|-----|-------|

| POR to Serial Interface                    |                          | T <sub>RDY</sub>                       |     |     | 15  | ms    |

| Ready                                      |                          | · KD1                                  |     |     | . • |       |

| Input to Output Delay in ZDB mode (matched |                          |                                        |     |     |     |       |

| pathways on external                       |                          | T <sub>ZDELAY</sub> [8]                |     | 100 |     | ps    |

| feedback, IN0 input,                       |                          |                                        |     |     |     | -     |

| IN3 feedback)                              |                          |                                        |     |     |     |       |

| Temperature Variation                      |                          | T [8]                                  |     |     | 1   | ps/C  |

| of delay in ZDB mode                       |                          | T <sub>ZDELAY,TMP</sub> <sup>[8]</sup> |     |     | Ī   | μ5/Ο  |

|                                            | Using a special mode     |                                        |     |     |     |       |

| One free run PLL clock                     | for fuse locked parts to | _                                      |     |     | 10  | ms    |

| on fuse locked parts                       | generate one free run    | START,Special                          |     |     | 10  | 1115  |

|                                            | output from one PLL      |                                        |     |     |     |       |

#### Notes:

- 1. 1 Hz Output Available only on output OUT0B (OUT0BP, OUT0BN). Range supported is 8 kHz to 2100 MHz for all the other outputs.

- 2. Hitless Switching enables PLL to switch between input clocks when the current clock is lost,

- a. Clock Loss can be defined as 2 / 4 / 8 / 16 consecutive missing pulses.

- b. Priority list for the input clocks can be set in the register map independently for each PLL.

- c. Output is truly hitless (no phase transient and 0 ppb relative error in frequency) for exactly same frequency input clocks that are switched.

- d. Hitless switching support is both revertive and non-revertive

- i. Revertive / Non-revertive Support: Assume Clock Input 0 is lost and switch is made to Clock Input 1. Then, PLL reverts to Clock Input 0 when it becomes valid again in Revertive mode. It does not switch back to Clock Input 0 even when it becomes valid again in the non-Revertive mode.

- 3. PLL enters holdover mode when the active input clock and all spare clocks in the clock priority list for hitless switching are lost,

- a. Clock Loss can be defined as 2 / 4 / 8 / 16 consecutive missing pulses

- b. Programmable Clock Loss settings ensure Gapped Clocks can be supported by choosing higher number of missing pulses as the trigger for clock being invalid

- c. Entering hold over mode is supported with the frequency frozen at a historical average determined from the H<sub>DELAY</sub> and H<sub>AVG</sub> settings.

- 4. For low PLL Loop Bandwidths, wake up time can be very large unless the speed up feature is used. The speed up feature provides the user options to use a completely independent loop bandwidth for the wake up transitioning to the regular bandwidth after frequency and phase are locked.

- a. Fast Lock Bandwidth needs to be less than 100 times smaller than the input clock frequency (divided input at PLL phase detector) for stable and bounded (in time) lock trajectory of the PLL

- 5. The 0.005 ppb specification is for the smallest frequency step resolution available. Larger frequency step resolutions up to 100 ppm can be used also. The frequency resolution for the DCO mode frequency step is independently programmable for each DCO step.

- All output clocks from one specific PLL are phase aligned. Relative delay adjustment is then possible on each clock individually as defined by the T<sub>RES</sub> parameter.

- 7. This test is for 2 inputs at 8M that are switched to get a 622.08M output.

- 8. Both input and feedback at 8 MHz with the delays exactly matched and same slew for both for the chip.

### **Table 9 Fault Monitoring Indicators**

| Description                                                          | Conditions                                                                                                                                                                     | Symbol                             | Min | Тур | Max  | Units  |

|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----|-----|------|--------|

| Clock Loss Indicator<br>Thresholds                                   | Clock Loss Indicators can be set on any of the four inputs. Loss of 2 / 4 / 8 / 16 consecutive pulses can be used to indicate a clock loss.  Programmable in the register map. | CL <sub>X</sub> [1,4]              | 2   | 4   | 16   | Pulses |

| Fine Frequency Drift Indicator Thresholds: Step Size                 | Frequency drift threshold is programmable in the                                                                                                                               |                                    |     | ±2  |      | ppm    |

| Fine Frequency Drift<br>Indicator<br>Thresholds: Hysteresis<br>Range | range with the step size resolution specified. Frequency drift hysteresis is                                                                                                   | FD <sub>X</sub> <sup>[2,3,4]</sup> | ±2  |     | ±500 | ppm    |

| Fine Frequency Drift Indicator Thresholds: Range                     | programmable in the range with the step size resolution specified.                                                                                                             |                                    | ±2  |     | ±500 | ppm    |

| Description                                    | Conditions                                                                                                                                                                                                        | Symbol | Min  | Тур | Max   | Units |

|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|-----|-------|-------|

| Coarse Frequency Drift<br>Indicator Thresholds | Coarse Drift Indicators programmable from<br>{Up to ±1600 ppm in steps of ± 100 ppm}                                                                                                                              |        | ±100 |     | ±1600 | ppm   |

| Lock Loss Indicator<br>Threshold               | Lock Loss Indicator threshold is programmable in the range specified from the following choices for setting and clearing LL: {±0.2, ±0.4} ppm, {±2, ±4} ppm, {±20, ±40} ppm, {±200, ±400} ppm, {±2000, ±4000} ppm | LL     | ±0.2 |     | ±4000 | ppm   |

#### Notes:

- 1. Clock Loss Indicators are used for:

- a. Hitless Switching Triggers

- b. Update in Status Registers in the register map

- Frequency Drift Indicators can use any one of the four inputs or the Crystal / Reference input as the golden reference with respect to which FDx for all other clocks can be recorded in the Status Registers. FDx thresholds for each clock input for each clock can be set independently.

- 3. Coarse and Fine Frequency Drift indicators can be concurrently enabled. This enables the user to detect fast drifting frequencies since detecting fine drifts will take longer measurements.

- 4. Clock loss and Lock loss indicators are available as alerts on flexible IO pins as described in the functional description section of the data sheet.

- 5. Clock Loss can be combined with either of the frequency drift monitors (coarse and fine) to trigger the hitless switching event in the PLLs. The trigger for a hitless switching event in the PLL can therefore be either the Clock Loss event or either of Clock Loss or Frequency Drift.

#### **Table 10 Crystal Requirements**

| Description                   | Conditions                                                                                                                    | Symbol                             | Min | Тур | Max | Units |

|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----|-----|-----|-------|

| High Fundamental Freq         | uency Crystal Reference                                                                                                       | (HFF)                              |     |     |     |       |

| Crystal Frequency             | Can be supported with a fundamental crystal of 100-160 MHz range.                                                             | XTAL <sub>IN</sub>                 | 100 |     | 160 | MHz   |

| C0 cap for crystal            |                                                                                                                               | XTAL <sub>C0</sub>                 |     |     | 2   | pF    |

| CL cap for crystal            | Small range around CL only                                                                                                    | XTALcL                             |     | 5   |     | pF    |

| ESR for crystal               | ESR defined at frequency of oscillation                                                                                       | XTALESR                            |     |     | 40  | Ω     |

| Rm1 for crystal               |                                                                                                                               | XTAL <sub>Rm1</sub>                |     |     | 20  | Ω     |

| Power delivered to crystal    | Drive Level to the crystal                                                                                                    | XTAL <sub>PWR</sub>                |     | 100 |     | μW    |

| <b>Third Overtone Crystal</b> | Reference (OT3)                                                                                                               |                                    |     |     |     |       |

| Crystal Frequency             | Can be supported with an OT3 crystal of 100-160 MHz range.                                                                    | XTAL <sub>IN</sub>                 | 100 |     | 160 | MHz   |

| C0 cap for crystal            |                                                                                                                               | XTAL <sub>C0</sub>                 |     |     | 2   | pF    |

| CL cap for crystal            | Small range around CL only                                                                                                    | XTALCL                             |     | 5   |     | pF    |

| ESR for crystal               | ESR defined at frequency of oscillation                                                                                       | XTAL <sub>ESR</sub> <sup>[1]</sup> |     |     | 80  | Ω     |

| Rm3 for crystal               |                                                                                                                               | XTAL <sub>Rm3</sub>                |     |     | 40  | Ω     |

| Power delivered to crystal    | Drive Level to the crystal                                                                                                    | XTAL <sub>PWR</sub>                |     | 100 |     | μW    |

| Low Frequency Fundan          | nental Crystal (LFF)                                                                                                          |                                    |     |     |     |       |

| Crystal Frequency             | Can be supported with<br>a fundamental crystal<br>> 37.5 MHz range. For<br>Best Performance use<br>an LFF crystal<br>> 48 MHz | XTAL <sub>IN</sub>                 | 48  |     | 54  | MHz   |

| Description                | Conditions                              | Symbol                  | Min | Тур | Max | Units |

|----------------------------|-----------------------------------------|-------------------------|-----|-----|-----|-------|

| C0 cap for crystal         |                                         | XTAL <sub>C0</sub>      |     |     | 2   | pF    |

| CL cap for crystal         | Small range around CL only              | XTAL <sub>CL</sub>      |     | 8   |     | pF    |